Die Toshiba Memory Corporation, der weltweit führende Anbieter von Speicherlösungen, hat heute die Entwicklung eines Brückenchips bekannt gegeben, mit dem SSDs mit hohen Geschwindigkeiten und großen Kapazitäten realisiert werden können. Mittels Brückenchips, die wenig Platz belegen und wenig Strom verbrauchen, konnte das Unternehmen erfolgreich mehr Flash-Speicherchips mit weniger Hochgeschwindigkeits-Signalleitungen verbinden als mit der konventionellen Methode ohne Brückenchips. Dieses Ergebnis wurde am 20. Februar in San Francisco auf der International Solid-State Circuits Conference 2019 (ISSCC 2019) bekannt gegeben.

Diese Pressemitteilung enthält multimediale Inhalte. Die vollständige Mitteilung hier ansehen: https://www.businesswire.com/news/home/20190221006079/de/

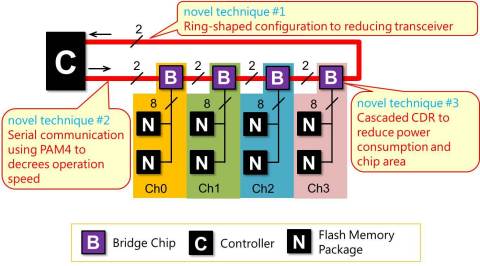

Fig. 1 Connection using bridge chips (Graphic: Business Wire)

Bei SSDs sind mehrere Flash-Speicherchips mit einem Controller verbunden, der ihren Betrieb verwaltet. Wenn mehr Flash-Speicherchips mit einer Controller-Schnittstelle verbunden sind, leidet die Betriebsgeschwindigkeit. Die Anzahl der Chips, die verbunden werden können, ist daher begrenzt. Um die Kapazität zu erhöhen, ist es erforderlich, die Anzahl der Schnittstellen zu erhöhen. Dies führt jedoch dazu, dass eine enorme Anzahl von Hochgeschwindigkeits-Signalleitungen mit dem Controller verbunden sind. So wird es schwieriger, die Leitungen auf der SSD-Baugruppe zu implementieren.

Das Unternehmen hat dieses Problem mit der Entwicklung eines Brückenchips gelöst, der den Controller und Flash-Speicherchips verbindet (Abb. 1), drei neuartige Techniken: eine Daisy-Chain-*1Verbindung mit dem Controller und Brückenchips in Ringform; eine serielle Übertragung mit PAM 4*2; sowie eine Jitter*3-Verbesserungstechnik, mit der ein PLL-Schaltkreis*4 in den Brückenchips entfällt. Mittels dieser Techniken können die Betriebskosten der Brückenchips gesenkt werden und es ist möglich, eine große Anzahl von Flash-Speicherchips mit hoher Geschwindigkeit mit nur wenigen Hochgeschwindigkeits-Signalleitungen zu betreiben (Abb. 2).

Aufgrund der ringförmigen Anordnung der Brückenchips und durch den Controller kann die Anzahl der im Brückenchip erforderlichen Sendeempfänger von zwei auf ein Paar gesenkt werden. Die Chipfläche des Brückenchips kann reduziert werden. Außerdem werden die Betriebsgeschwindigkeit in den Schaltkreisen der Brückenchips durch serielle PAM-4-Übertragung zwischen dem Controller und den per Daisy-Chain verbundenen Brückenchips gesenkt und die erforderliche Leistung entspannt. Durch einen neuen CDR*5, der die Eigenschaften von PAM 4 zur Verbesserung der Jittereigenschaften nutzt, fällt die Notwendigkeit eines PLL-Schaltkreises im Brückenchip weg. Dies trägt auch zu einer kleineren Chipfläche sowie einem geringerem Energieverbrauch bei.

Die Prototyp-Brückenchips wurden mittels des 28nm-CMOS-Verfahrens hergestellt und die Ergebnisse wurden durch Verbindung von vier Brückenchips und einem Controller in einer ringförmigen Daisy-Chain überprüft. So konnten die zufriedenstellende Leistung der PAM-4-Übertragung durch alle Brückenchips und den Controller mit 25,6 Gbps sowie die Tatsache bestätigt werden, dass es möglich ist, eine BER*6 von weniger als 10-12 zu erzielen.

In Zukunft wird das Unternehmen seine Entwicklungsarbeit hin zu Speicher mit hohen Geschwindigkeiten und großen Kapazitäten auf ungekanntem Niveau fortsetzen. Dazu sollen die Leistung der Brückenchips weiter verbessert und gleichzeitig Fläche und Stromverbrauch des Chips reduziert werden.

Hinweise

*1 Daisy-Chain: ein Verbindungsschema, bei dem mehrere Chips in Reihe geschaltet sind

*2 PAM 4: Vier-Stufen-Pulsamplitudenmodulation (enthält vierstellige Daten)

*3 Jitter: Fluktuation bei der Zeitdomäne von Uhr oder Signal-Wellenformen

*4 PLL: Phase Locked Loop (ein Schaltkreis, der ein präzises Referenzsignal generiert)

*5 CDR: Clock Data Recovery (ein Schaltkreis, der Daten und Taktung des enthaltenen Signals wiederherstellt)

*6 BER: Bit Error Rate (ein geringerer Wert bedeutet bessere Leistung)

Über die Toshiba Memory Corporation

Die Toshiba Memory Corporation, ein weltweit führender Anbieter von Speicherlösungen, spezialisiert sich auf die Entwicklung, die Produktion und den Vertrieb von Flash-Speichern und SSDs. Im Juni 2018 wurde Toshiba Memory von einem Industriekonsortium übernommen, das von Bain Capital geleitet wird. Toshiba Memory ist ein Wegbereiter für innovative Speicherlösungen und Dienstleistungen, die das Leben der Menschen bereichern und den Horizont der Gesellschaft erweitern. BiCS FLASH, die innovative 3D-Flash-Speichertechnologie des Unternehmens, prägt die Zukunft des Speichers in High-Density-Anwendungen wie z. B. in leistungsfähigeren Smartphones, PCs, SSDs, Automobil- und Rechenzentren. Erfahren Sie mehr über Toshiba Memory unter https://business.toshiba-memory.com/en-apac/top.html

Die Ausgangssprache, in der der Originaltext veröffentlicht wird, ist die offizielle und autorisierte Version. Übersetzungen werden zur besseren Verständigung mitgeliefert. Nur die Sprachversion, die im Original veröffentlicht wurde, ist rechtsgültig. Gleichen Sie deshalb Übersetzungen mit der originalen Sprachversion der Veröffentlichung ab.

Originalversion auf businesswire.com ansehen: https://www.businesswire.com/news/home/20190221006079/de/

Contacts:

Toshiba Memory Corporation

Kota Yamaji

Abteilung Geschäftsplanung

Telefon: +81-3-6478-2319

semicon-NR-mailbox@ml.toshiba.co.jp